Transistorudvikling: Fra plan til CFET, 3D-integration omdefinerer halvlederfremskridt

I mere end et halvt århundrede voksede halvlederindustrien ved at følge en simpel regel: Gør transistorer mindre.Krympende funktionsstørrelser leverede højere ydeevne, lavere effekt og lavere omkostninger pr. transistor.Men i dag har denne vej nået sin fysiske og økonomiske grænse.Æraen med ren skalering er forbi, og en ny æra af strukturel innovation og 3D-integration er begyndt.

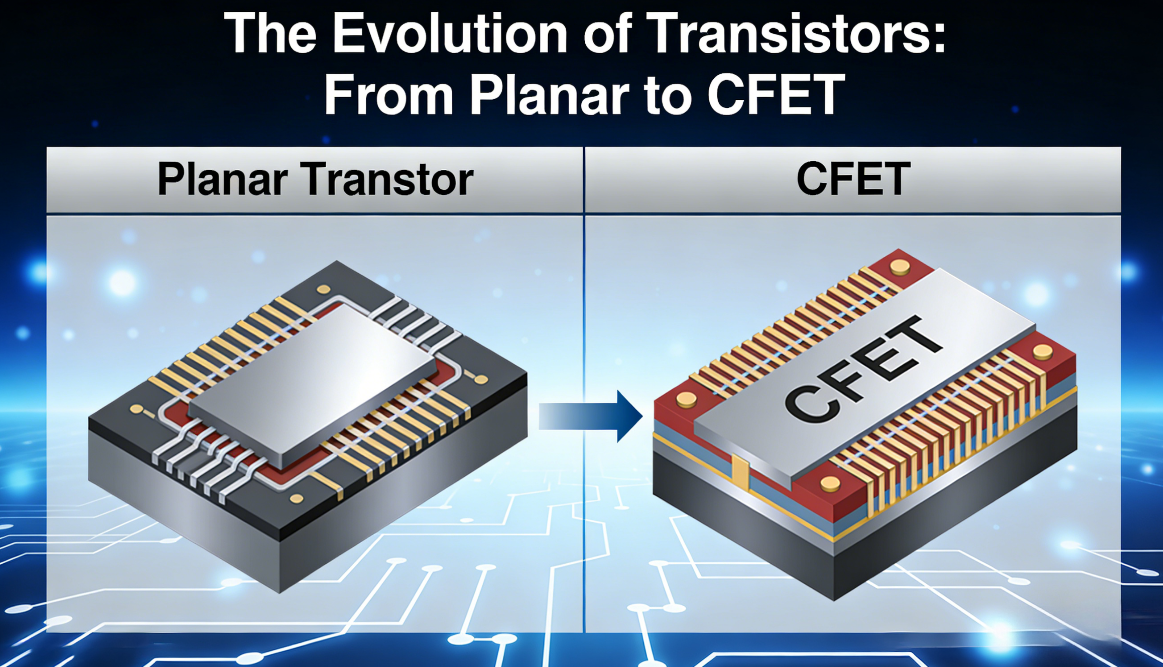

Selve transistoren gennemgår en komplet arkitektonisk revolution.Fra plan MOSFET til FinFET, fra GAA nanosheet til CFET-stabling, repræsenterer hvert trin et skift fra krympende til ombygning af transistoren i tre dimensioner.Dette er ikke kun trinvis forbedring – det er en komplet omdefinering af, hvordan chips leverer ydeevne.

De fire generationer af transistorarkitektur

1. Plan transistor (traditionel 2D)

Den klassiske flade struktur, hvor porten styrer kanalen fra oven.Det dominerede fra de tidlige dage ned til 40nm og 28nm.Efterhånden som dimensionerne skrumpede yderligere, blev lækstrøm og elektrostatisk kontrol uløselige problemer.

2. FinFET (3D Gate Control)

Kanalen bliver en lodret "finne", hvor porten vikler sig rundt om tre sider.Dette forbedrer den elektrostatiske kontrol drastisk, reducerer lækage og muliggør nedskalering til 7nm, 5nm og endda 3nm.FinFET blev grundlaget for den moderne højtydende chip-æra.

3. GAA Nanosheet (Gate-All-Around)

Ved 2nm og derunder rammer FinFET sin grænse.GAA erstatter finnen med stablede vandrette nanotråde eller plader, helt omgivet af porten.Det giver bedre kontrol, lavere effekt og højere drivstrøm.GAA er nu den almindelige struktur for 2nm-klasse chips på tværs af TSMC, Samsung og Intel.

4. CFET (Supplerende FET)

Den næste grænse: stabling af NMOS og PMOS lodret.CFET pakker to transistorer i fodaftrykket af én, hvilket drastisk reducerer arealet og forbedrer tætheden.Det er den ultimative evolutionære ende af transistorskalering, før ægte 3D-systemintegration tager over.

Hvorfor skalering alene ikke længere virker

- Procesomkostningerne stiger eksponentielt ved hver ny knude

- Kvantelækage og fysiske begrænsninger hærder grænserne

- Sammenkoblingsforsinkelse og strømforbrug overhaler transistorhastigheden

- Store monolitiske spåner lider under lavt udbytte og høje omkostninger

Industrien har indset: Ydelse kommer ikke længere fra mindre transistorer.Det kommer fra bedre forbindelser, smartere arkitektur og vertikal integration.

The New Era: Tre lag af 3D-innovation

Halvlederfremskridt er nu defineret af tre dimensioner af 3D-design:

- 3D transistor: FinFET, GAA, CFET – opbygning af transistoren lodret

- 3D-enhedsstabling: Hukommelse på logik, hybridbinding, SRAM-stabling

- 3D systemintegration: Chiplet, 2,5D/3D-emballage, interposer-baseret integration

Sammen danner de 3D×3D×3D æra: transistoren, enheden og systemet bliver alle tredimensionelle.

DTCO: Den nye kernekompetence

Når skaleringen slutter, Design Technology Co-Optimization (DTCO) bliver kritisk.Det betyder co-design af arkitektur, transistorstruktur, metal routing og pakning fra starten.De stærkeste virksomheder er ikke længere kun procesledere – de er integratorer på systemniveau.

Ledningseffektivitet, strømforsyning, termisk design og båndbreddetæthed bestemmer nu den reelle produktydelse.

AI er den ultimative drivkraft

AI og højtydende databehandling kræver hidtil uset båndbredde, energieffektivitet og tæthed.Disse krav kan ikke opfyldes ved traditionel skalering.De kræver:

- Ultra-høj båndbredde hukommelse-compute interconnect

- Ekstrem energieffektivitet pr. operation

- Massiv parallelitet og tæt integration

AI har tvunget hele industrien til at opgive ren skalering og omfavne fuld 3D heterogen integration.

Konklusion: Fremtiden er ikke mindre, den er højere

Tiden med krympende transistorer er ved at falme.Fremtiden for halvledere handler ikke om at gøre enheder mindre – det handler om at bygge systemer højere, tættere og mere intelligent forbundet.

Fra Planar til FinFET til GAA til CFET har transistoren fuldført sin udvikling.Den næste kamp vil blive udkæmpet 3D-integration, avanceret emballage og design på systemniveau.Det er her det næste årti med halvlederledelse vil blive afgjort.